邢臺勝博興業建材科技 誠信為本,打造2W樓承板專業品牌

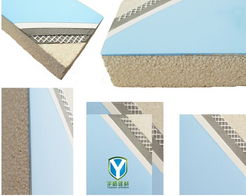

在建筑行業快速發展的今天,優質的建筑材料是保障工程安全與質量的核心。邢臺勝博興業建材科技有限公司作為一家專注于建筑材料生產的企業,以其誠信經營的理念和卓越的產品質量,贏得了市場的高度認可。特別是在樓承板領域,公司推出的2W樓承板系列產品,憑借出色的承重性能、耐久性和環保特性,成為眾多建筑項目的首選。

勝博興業建材科技始終將誠信視為企業發展的基石。從原材料采購到生產加工,再到售后服務,公司嚴格遵循國家標準和行業規范,確保每一塊樓承板都達到優質水準。通過引進先進的生產設備和工藝,公司不僅提升了2W樓承板的強度和穩定性,還優化了其安裝便捷性,幫助客戶縮短工期、降低成本。

除了產品優勢,勝博興業還注重與客戶的長期合作。公司提供定制化解決方案,根據項目需求調整樓承板的規格和性能,確保完美匹配各類建筑結構。同時,完善的售后服務體系讓客戶無后顧之憂,進一步鞏固了企業在邢臺及周邊地區的信譽。

在綠色建筑趨勢下,勝博興業積極研發環保型樓承板,采用可回收材料和生產工藝,減少對環境的影響。這不僅響應了國家可持續發展的號召,也為客戶提供了更安全、健康的選擇。

邢臺勝博興業建材科技以誠信和專業精神,持續推動建筑材料行業的進步。無論是大型商業綜合體還是住宅項目,其2W樓承板都展現出可靠的價值。選擇勝博興業,就是選擇質量與信任的保障。

如若轉載,請注明出處:http://www.fzz8.cn/product/19.html

更新時間:2026-04-13 01:05:58